Программирование и отладка логики ПЛИС на стенде NanoBoard

Для программирования коммутации ПЛИС и отладки логики FPGAпроекта фирмой Altium Ltd разработано семейство отладочных стендов NanoBoard, использование которых превращает программноаппаратный комплекс Altium Designer в «инновационную станцию» (Altium Innovation Station), на которой может быть выполнен полный цикл разработки проекта ПЛИС, включая программирование тиража микросхем для установки их в поставляемые заказчику печатные платы.

Ресурсы NanoBoard

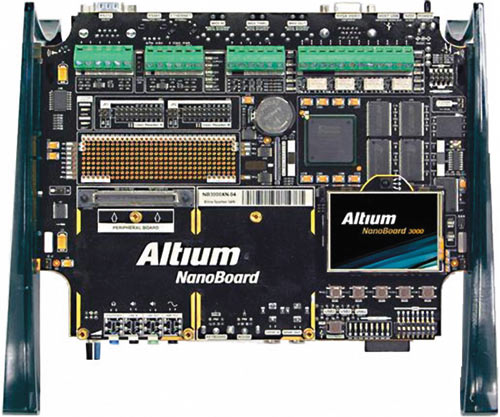

На рынок последовательно поступали стенды NanoBoard NB1, NanoBoard NB2DSK01 и NanoBoard 30001 (рис. 1). По сути, каждая из моделей представляет собой компьютер с развитой периферией и средствами подключения отлаживаемой микросхемы к аппаратным средствам стенда.

Сердцем отладочного стенда является контроллер, осуществляющий связь исполняемого FPGAпроекта Altium Designer с «физической» микросхемой ПЛИС, установленной на стенде для программирования коммутации и отладки логики проекта. Протокол обмена данными Altium Designer с отладочным стендом NanoBoard, разработанный фирмой Altium Ltd, носит название NanoTalk, а контроллер стенда называется NanoTalk Controller.

В моделях NanoBoard NB1 и NanoBoard NB2DSK01 отлаживаемая ПЛИС устанавливается на сменных «дочерних» платах (Daughter Board), а на материнской плате стенда располагаются только контроллер, управляющий процессом отладки и программирования коммутации ПЛИС, органы индикации, средства, имитирующие связь ПЛИС с ее внешним окружением в проектируемом функциональном узле, и средства последовательного наращивания, обеспечивающие возможность использования сразу нескольких стендов NanoBoard в одной конфигурации.

Рис. 1. Отладочный стенд NanoBoard 3000

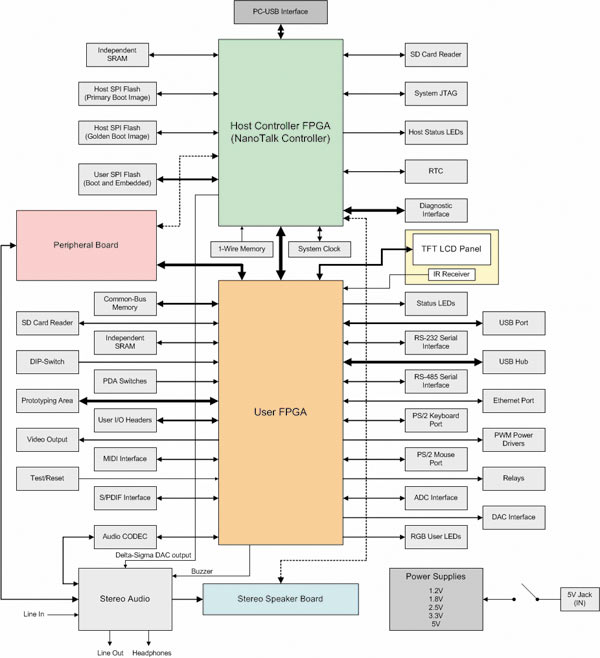

В моделях семейства NanoBoard 3000 на материнской плате стенда смонтирована микросхема ПЛИС одного из трех производителей — фирмы Xilinx (NanoBoard 3000XN), Altera (NanoBoard 3000AL) или Lattice (NanoBoard 3000LC), которая названа пользовательской ПЛИС (User FPGA) и может применяться в качестве одной из реализаций FPGAпроекта (рис. 2).

Рис. 2. Структурная схема NanoBoard 3000

В данной публикации мы постараемся осветить функциональные возможности и технологию использования отладочного стенда NanoBoard 3000AL с предустановленной «пользовательской» ПЛИС от фирмы Altera EP3C40F780C8N. На случай, если пользователь реализует проект на ПЛИС другого типа, на материнской плате предусмотрена возможность установить эту пользовательскую ПЛИС на сменной «периферийной» плате (Peripheral Board).

Связь стендов NanoBoard с ПК осуществляется через стандартный USBпорт по мультиплексированному каналу JTAGинтерфейса. По этому каналу в ПК и из него передается информация, служащая для управления работой контроллера стенда (NanoTalk Channel), программирования внутренней коммутации пользовательской ПЛИС (Hard Devices Channel) и загрузкой в пользовательскую ПЛИС программного приложения в случае проектирования микроконтроллеров или микроЭВМ (Soft Devices Channel). При подключении стенда NanoBoard к ПК с работающей программой Altium Designer автоматически активируется драйвер, опознающий наличие и идентифицирующий версию NanoBoard и периферийной платы (если она подключена), а также устанавливающий связь активного FPGAпроекта с ресурсами NanoBoard.

Для обнаружения и идентификации версии NanoBoard и периферийной платы на них устанавливаются ПЗУ (1Wire Memory), в которые занесен 40байтовый идентификационный код, состоящий из четырех полей:

- <UniqueID> — уникальный идентификатор, присвоенный изготовителем, — обозначение типа и серийный номер микросхемы ПЗУ;

- <ClassID> — обозначение типа и версии (revision) стенда NanoBoard или периферийной платы;

- <BatchID> — номер партии продукта;

- <VendorID> — обозначение производителя стенда NanoBoard или периферийной платы (фирма Altium обозначается кодом 00000001h).

Взаимодействие FPGAпроекта с ресурсами NanoBoard

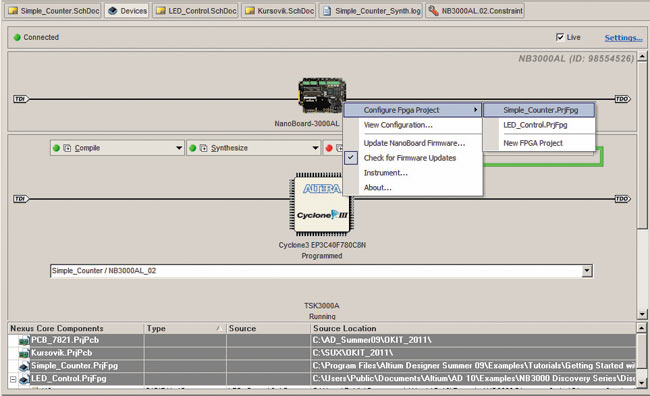

Доступ активного FPGAпроекта к ресурсам NanoBoard, в том числе к пользовательской ПЛИС, происходит из оболочки Devices View в моде Live.

Для обеспечения доступа должна быть сформирована конфигурация проекта. Это, как уже говорилось, именованный список файлов привязки (Constraint files). Файлы привязки, описывающие ресурсы NanoBoard, как и конфигурация, могут быть сформированы вручную, однако Altium Designer предоставляет возможность облегчить эту трудоемкую работу путем автоматического формирования конфигурации. Для этого нужно щелчком правой клавиши мыши на значке NanoBoard в панели Devices View активировать контекстное меню и указать в нем команду Configure FPGA Project (рис. 3). В открывающемся подменю выбрать один из списка загруженных проектов или указать команду New FPGA Project (Создать новый FPGAпроект).

Рис. 3. Панель Devices View

При выборе имени существующего проекта программа находит файлы привязок, загруженные при инсталляции Altium Designer в директорию ..\Library\FPGA\, и автоматически подключает их к проекту в соответствии с обнаруженным системой идентификационным кодом NanoBoard, а именно его полем ClassID. Так, при обнаружении системой стенда NanoBoard 3000 с идентификационным кодом <ClassID> = NB3000AL.02 программа извлекает из директории файл NB3000AL.02.Constraint. При обнаружении периферийной платы PB30.01 программа дополнительно подключает к FPGAпроекту файл привязок PB30.01.Constraint.

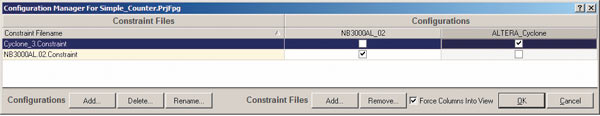

Командой главного меню

Project -> Configuration Manager или командой View Configuration из того же контекстного меню открывается диалог просмотра и редактирования конфигурации проекта (рис. 4).

Рис. 4. Диалог настройки конфигурации FPGA-проекта

В случае использования отладочной периферийной платы программа автоматически формирует и включает в конфигурацию файл привязок, содержащий описание подключений периферийной платы к материнской плате NanoBoard 3000. Имя файла — NB3000AL_02_BoardMapping.Constraint, и сохраняется он в той же директории, что и файл проекта *.PrjFpg.

Порткомпоненты

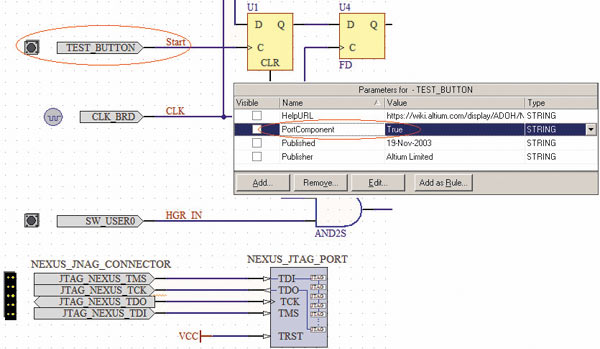

Для осуществления электрической связи цепей внешнего окружения с цепями логического ядра в схеме FPGAпроекта к ним в схемных документах PCB и FPGAпроектов подключаются одноименные метки Port. Далее в файлах привязок (Constraint) назначается подключение этих цепей к контактам выбранной ПЛИС. В случае работы с отладочным стендом NanoBoard 3000 подключение внешних выводов «пользовательской» ПЛИС выполнено печатным монтажом на материнской плате, поэтому нет необходимости подключать к внешним связям схемы FPGAпроекта стандартные порты и назначать их привязку к выводам «пользовательской» ПЛИС. Вместо этого для обеспечения возможности имитации сигналов внешнего окружения ПЛИС в Altium Designer сформированы библиотеки специальных интерфейсных компонентов, которые должны быть включены в схемный документ FPGAпроекта (рис. 5). Эти компоненты, называемые в терминологии Altium Designer порткомпонентами, размещены (для NanoBoard 3000) в библиотеке ..\Library\FPGA\FPGA NB3000 PortPlugin.IntLib.

Рис. 5. Пример порт-компонентов в схемном документе FPGA-проекта

Эти интерфейсные компоненты обеспечивают автоматическое подключение ресурсов NanoBoard к входным/выходным контактам пользовательской микросхемы ПЛИС и по присвоенному им по умолчанию параметру PortComponent True распознаются программой как внешние по отношению к FPGAпроекту.

Компоненты Nexus_JTAG_Connector и Nexus_JTAG_Port обеспечивают доступ Altium Designer к встроенным в пользовательскую ПЛИС программным приложениям и виртуальным инструментам отладки. Сигналы, циркулирующие по этим цепям, порождаются контроллером стенда и подводятся к четырем предопределенным контактам пользовательской ПЛИС.

Порткомпоненты могут быть конвертированы в обычные метки цепей Port по команде главного меню Tools -> Convert -> Convert Parts To Ports с последующим щелчком левой кнопки мыши на выбранном компоненте либо командой Part Actions -> Convert Parts To Ports из контекстного меню, активируемого щелчком правой кнопки на выбранном компоненте. Они также автоматически конвертируются в стандартные метки Port при выполнении синтеза проекта, обеспечивая связность логического ядра проекта с цепями внешнего окружения ПЛИС при объединении FPGA и PCBпроектов.

Программирование FPGAпроекта на пользовательской ПЛИС стенда NanoBoard 3000

Рассмотрим стадии программирования ПЛИС на примере проекта кольцевого счетчика, приводимого в директории пакета ..\Examples\Tutorials\Getting Started with FPGA Design\Simple Counter.PrjFpg.

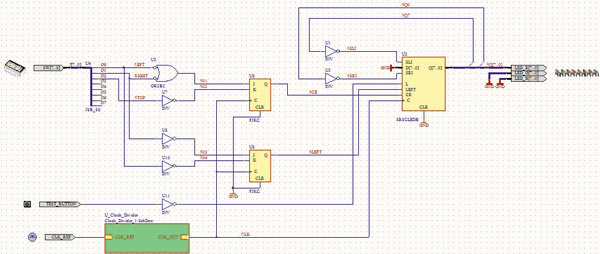

Рис. 6. Функциональная схема кольцевого счетчика

Функциональная схема кольцевого счетчика с коэффициентом пересчета 8 построена на базе следующих логических прототипов из библиотеки FPGA Generic.IntLib (рис. 6):

- двунаправленного восьмиразрядного регистра сдвига SR8CLEDB;

- двух JK триггеров FJKC;

- шести инверторов INV;

- дизъюнктора (схема ИЛИ) низких логических уровней OR2B2;

- разветвителя шины J8B_8S.

Для проверки правильности функционирования и демонстрации работы счетчика на стенде NanoBoard 3000 ко входам логики и выходам регистра подключены следующие порткомпоненты из библиотеки FPGA NB3000 PortPlugin.IntLib:

- CLK_REF — интерфейс с тактовым генератором стенда NanoBoard с частотой 20 МГц;

- TEST_BUTTON — кнопка общего сброса TEST/RESET;

- DIPSWITCH — DIPблок из восьми переключателей (SW8);

- LEDS_RGB — блок 3Ѕ8 пользовательских светодиодов красного, зеленого и синего цветов (RGB USER LEDS).

Для того чтобы мелькание светодиодов, подключенных к выходам разрядов регистра, воспринималось глазом, в схему введен делитель частоты U_Clock_Divider с коэффициентом деления 10 млн (частота импульсов на выходе CLK_OUT составляет 2 Гц). Делитель частоты построен на семи последовательно соединенных делителях CDIV10DC50, оформлен как иерархический схемный элемент и входит в дерево документов проекта под именем Clock_Divider_1.SchDoc (рис. 7). В качестве альтернативного варианта делитель частоты может быть построен в виде HDLфайла в конструкциях языка описания аппаратуры VHDL и также включен в общую схему проекта как иерархический элемент.

Рис. 7. Дерево документов FPGA-проекта

После сохранения и компиляции документов проекта следует выполнить программирование внутренней коммутации ПЛИС:

- командой View -> Devices View открыть оболочку Devices;

- командой контекстного меню Configure FPGA Project (см. рис. 3) сформировать конфигурацию проекта (имя конфигурации NB3000AL_02). В дерево проекта программа включает файл привязок NB3000AL.02.Constraint;

- щелчком правой кнопки мыши на значке с изображением ПЛИС в поле Hard Devices Chain активировать контекстное меню и указать команду Reset — сброс коммутации, ранее занесенной в ПЛИС;

- выполнить последовательные стадии обработки проекта:

- Compile — компиляцию документов проекта,

- Synthesize — синтез промежуточного VHDLописания *.vhd и исходного файла описания схемы *.edn в обменном формате EDIF для программирования в среде САПР производителя ПЛИС (Vendor Tools). Оба файла, а также файл протокола *.log включаются программой в дерево документов проекта,

- Build — трансляция логической структуры проекта в логические примитивы ПЛИС и формирование файла программирования коммутации внутренней структуры ПЛИС,

- Program FPGA — загрузка файла программирования в микросхему ПЛИС на панели стенда NanoBoard 3000 или на съемной отладочной плате PB30.

Процесс выполнения всех фаз обработки проекта сопровождается выводом сообщений в панель Messages. Кроме того, подробная информация о выполнении всех фаз обработки, включая сообщения САПР Vendor Tools (в нашем случае это программа Altera QUARTUS II), отображается в панели Output.

По окончании загрузки программы коммутации надпись Reset (Сброшено) под значком микросхемы ПЛИС в панели Devices View заменяется на Programmed (Запрограммировано), а на материнской панели NanoBoard загорается светодиод LED2 PGM (Programmed). Можно запускать счетчик и проверять его работу:

- кнопкой Test/Reset триггеры счетчика сбрасываются в нулевое состояние;

- перемещением движка одного из переключателей SW6 или SW7 в положение ON (включено) запускается счет слева направо или справа налево. Светодиоды RGB_USER_LEDS отображают перемещение «единиц» и «нулей» по разрядам счетчика;

- перемещением движка переключателя SW5 в положение ON счет останавливается, если при этом переключатели SW6 или SW7 переведены в положение OFF (выключено).

Отметим, что микросхемы ПЛИС семейства Altera Cyclone III допускают многократное перепрограммирование коммутации, но не содержат в своей структуре энергонезависимого ПЗУ, в котором хранилась бы эта программа. Для этой цели в аппаратуре пользователя программа коммутации заносится в конфигурационное ПЗУ. Программа коммутации логики ПЛИС, занесенная в нее на стенде NanoBoard 3000, действует до тех пор, пока включено питание, а после выключения питания теряется. Поэтому для повторного запуска проекта на стенде NanoBoard 3000 требуется повторная загрузка программы коммутации в оболочке Devices View.

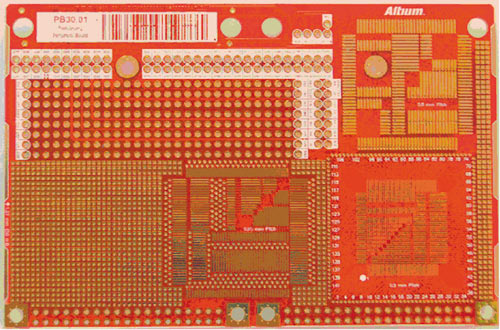

Рис. 8. Периферийная плата PB30

Периферийная плата PB30

Для работы совместно со стендом NanoBoard 3000 фирма Altium Ltd выпускает семейство периферийных плат для различных приложений. Нас в этом семействе интересует отладочная (Prototyping) периферийная плата PB30 (рис. 8), на которой отсутствуют ресурсы в обычном понимании. Это пустая печатная плата, на которой выполнены контактные площадки для монтажа SMD или штыревых ПЛИСкомпонентов пользователя, подлежащих программированию коммутации и отладке логики. Контактные площадки сгруппированы в пять полей с шагом расположения выводов 0,5, 0,65, 0,8, 1,27 и 2,54 мм. Для соединения с материнской платой NanoBoard 3000 на плату PB30 устанавливается 100контактная розетка электрического соединителя MOLEX540751009. Выводы пользовательской ПЛИС соединяются с контактами соединителя проводным монтажом.

Для опознания платы PB30 в конфигурации NanoBoard на ней устанавливается идентификационное ПЗУ DS2502P2.

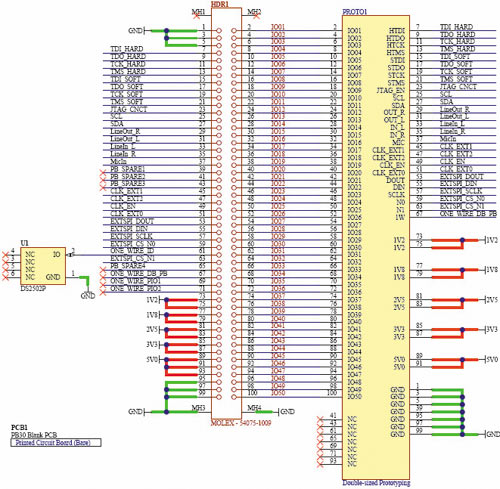

Приведем функциональную схему платы PB30 (рис. 9).

Рис. 9. Схема электрическая функциональная платы PB30

В приведенной схеме:

- U1 — идентификационное ПЗУ DS2502P;

- HDR1 — розетка соединителя MOLEX5407510009;

- PROTO1 — печатная плата с контактными площадками для монтажа пользовательской ПЛИС.

Видно, что 50 контактов соединителя (с четными номерами) могут быть соединены с 50 входнымивыходными выводами ПЛИС, установленной на плате, 34 контакта используются для подключения цепей питания и земли, к 26 контактам с материнской платы NanoBoard подводятся сигналы JTAGинтерфейса, тактовые сигналы и интерфейсные сигналы в ряде других стандартов.

Для обеспечения доступа сигналов логической схемы FPGAпроекта к микросхеме ПЛИС на периферийной плате в схемный документ проекта должен быть введен интерфейсный порткомпонент NANOCON50IOB, отображающий

50 пользовательских контактов соединителя периферийной платы PB30 с материнской платой NanoBoard 3000 (рис. 10).

Рис. 10. Порт-компонент соединителя платы PB30

В заключение отметим достоинства и недостатки рассмотренной конфигурации инновационной станции, объединяющей программный комплекс Altium Designer с ресурсами отладочного стенда NanoBoard 3000.

К достоинствам следует отнести наличие развитой периферии, реализованной на материнской плате NanoBoard 3000. Это позволяет разрабатывать и отлаживать сложные иерархические FPGAпроекты, включающие на нижнем уровне иерархии проекты таких ядер (Core Project), как контроллеры интерфейса RS232, RS485 USB, Ethernet и других протоколов, контроллеры клавиатуры, дисплея, АЦП/ЦАП, цифрового вводавывода аудиосигнала и др.

Вместе с тем можно отметить и ряд недостатков, ограничивающих сложность проектов, которые можно разработать в рассматриваемой среде:

- наличие на материнской плате NanoBoard 3000AL несменяемой пользовательской ПЛИС Altera Cyclone III EP3C40F780C8N позволяет разрабатывать и отлаживать FPGAпроекты только на этой микросхеме;

- эта пользовательская ПЛИС имеет 780 контактов, из которых 535 доступны для программирования пользователем, в то время как в настоящий момент на рынок поступают микросхемы ПЛИС с числом выводов 1000 и более;

- съемная периферийная плата PB30 дает возможность разработки проектов на микросхемах других семейств и типов от того же производителя — фирмы Altera, но для программирования пользователю доступны только 50 входныхвыходных контактов пользовательской ПЛИС — этого не хватает для всех возможных способов применения;

- при обработке проекта в оболочке Devices View не полностью используются ресурсы САПР Vendor Tools, в частности не выполняется оптимизация трассировки внутренних соединений и временных задержек.

Таким образом, возможность разработки и отладки проектов ПЛИС в среде Altium Designer не отменяет и не подменяет собой разработку проектов в среде САПР ведущих производителей ПЛИС.

При этом несомненным достоинством рассмотренной технологии является возможность выполнения сквозного проекта радиоэлектронного функционального узла на печатной плате, объединяющего в своей иерархии PCBпроект, подчиненный ему один или несколько FPGAпроектов, вложенные в FPGA Core и Embeddedпроекты.

1 Подробная информация — на интернетсайте www.altium.com/nanoboard.

2 Подробное описание см. на интернетсайте www.maximic.com.