Разработчикам печатных плат приходится учитывать огромное количество нюансов и деталей в своей работе. Вероятность ошибок в сложных проектах достаточно высока, а цена ошибок — значительна. Неточности проектирования могут привести к нарушению целостности сигналов и в дальнейшем вызвать трудности при производстве изделий. В результате растягиваются сроки сдачи проекта, увеличивается срок выхода готового продукта на рынок. Как минимизировать вероятность ошибок при проектировании печатных плат? Настроить систему электрических ограничений, причем на ранних этапах проектирования. Это позволит избежать ошибок и восполнить время, затраченное на настройку.

Богдан Филипов, менеджер по продукции, АО «Нанософт»

Зачем устанавливать ограничения

Внедрение ограничений в проекты позволяет избежать трех основных проблем:

- ошибочных действий человека;

- недостаточной проработки проекта на начальном этапе;

- работы в жестких временных рамках.

Устанавливая ограничения, разработчик закладывает основу для качественного и эффективного проектирования изделий, а взамен указанных проблем получает:

- снижение затрат на разработку;

- минимальное количество исправлений и ревизий перед сдачей проекта;

- сокращение времени выхода готового продукта на рынок.

Традиционные или новые методологии?

Еще недавно разработчики применяли правила проектирования в основном на этапе трассировки. Чтобы контролировать зазоры на плате, они использовали размерную сетку. Например, сетка с шагом 0,1 мм позволяла трассировать проводники с технологией 0,1/0,1 (ширина проводника/зазор между проводниками). Такой подход корректен, если ко всем проводникам предъявляются одинаковые требования по ширине и зазору, но современные проекты отличаются более сложными и разнообразными требованиями.

Распространенный в прошлом метод — проектирование и трассировка с отключенной системой контроля правил проектирования DRC (Design Rule Cheсking). Разработчики могли быстро создавать проекты печатных плат, учитывая возможные ошибки, которые они идентифицировали и устраняли только на последнем этапе работы.

Современные САПР печатных плат — альтернатива устаревшим методам. С помощью этих мощных и интуитивно понятных инструментов разработки можно эффективно и с наименьшими временными затратами настроить электрические ограничения.

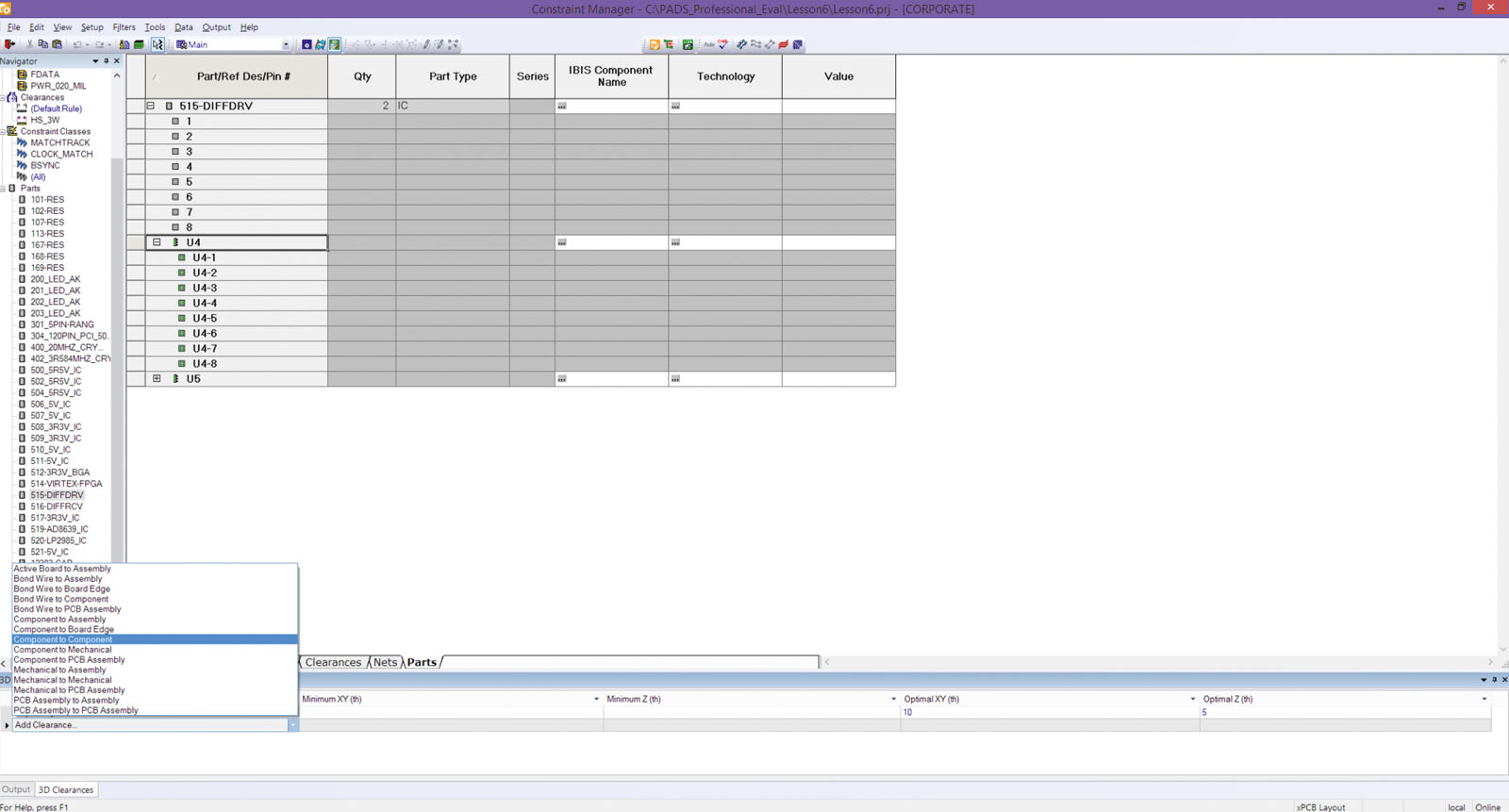

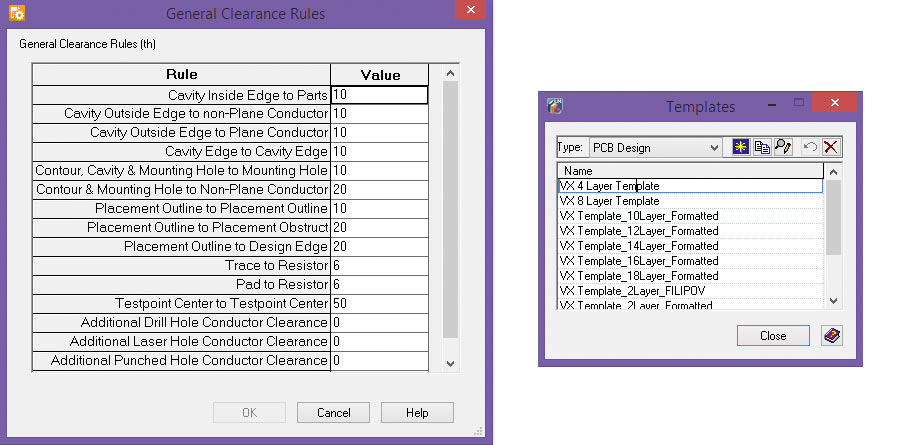

Некоторые САПР используют основанную на табличном представлении систему ввода ограничений (рис. 1), которая обновляется в режиме реального времени независимо от того, находится пользователь в схемотехническом или топологическом редакторе. Таким образом инженерсхемотехник может взаимодействовать с разработчиком топологии и задавать сквозные правила ограничений. Контроль правил в реальном времени (Online DRC) помогает разработчикам выполнить трассировку быстрее и качественнее. Нарушения и ошибки выявляются и устраняются по ходу проектирования, в результате сокращается время финальной верификации проекта.

Рис. 1. Интерактивная система ввода электрических ограничений

на основе электронных таблиц

Планирование ограничений

Пользовательский интерфейс может стать причиной затруднений в процессе разработки плат. Чтобы избежать этого, необходимо вводить ограничения на этапе планирования проекта. Такой подход позволяет инженеру работать непрерывно на протяжении всего цикла проектирования и не отвлекаться на проверку правил. Настройка правил на стадии подготовки проекта занимает время, но в перспективе обеспечивает повышение производительности на этапе проектирования. Важно помнить о том, что правила проектирования могут быть заданы до того, как будет производится трассировка.

Эффективные методы настройки ограничений

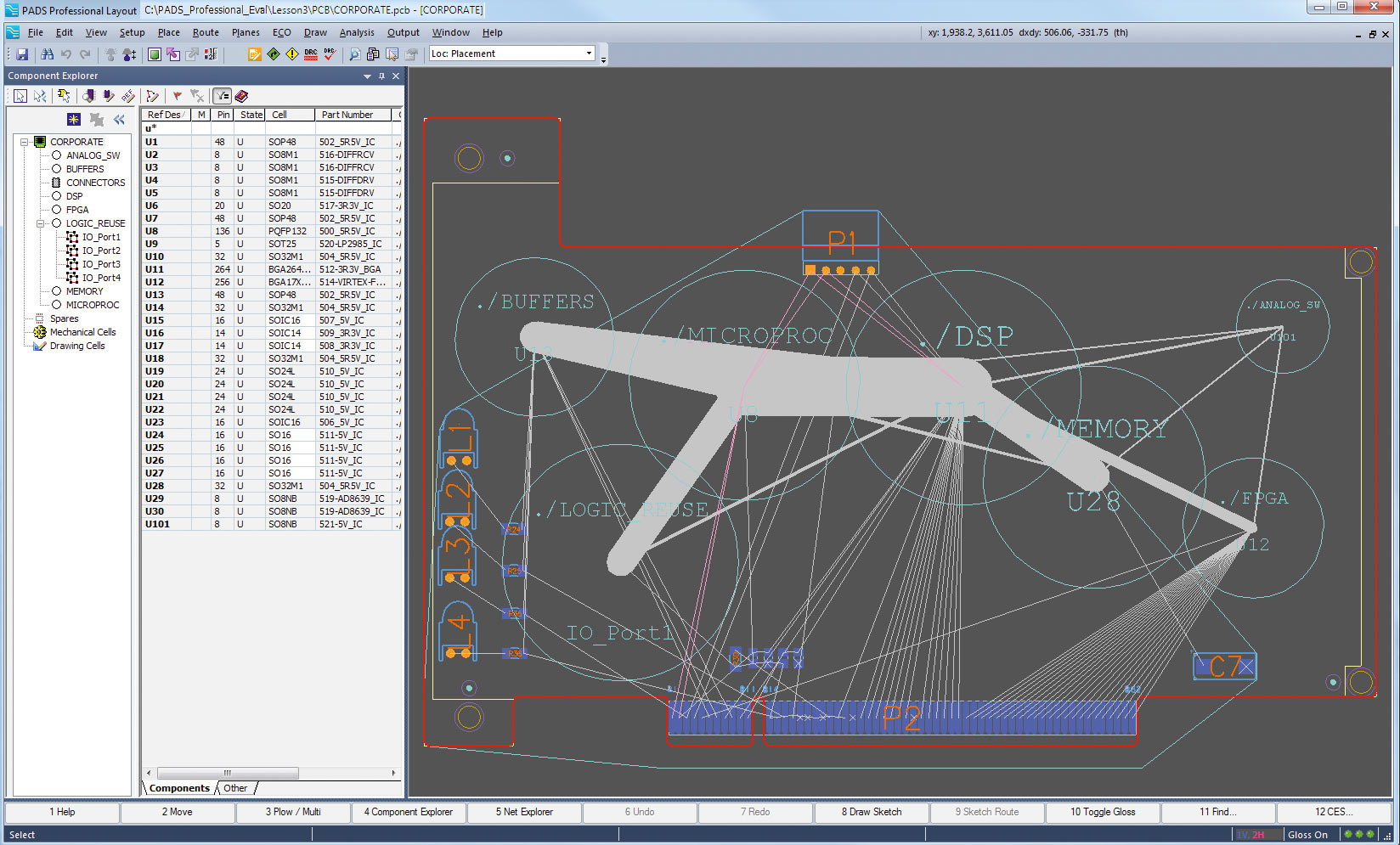

Цель ввода ограничений — заложить основу для качественной трассировки печатных плат. Какой способ настройки ограничений оптимален? Прежде всего на подготовительном этапе необходимо продумать, как сгруппировать и расположить компоненты на плате (рис. 2).

Рис. 2. Создание групп размещения в PADS позволяет ускорить этап компоновки печатной платы

Следующие восемь шагов позволят настроить систему ограничений быстро и эффективно:

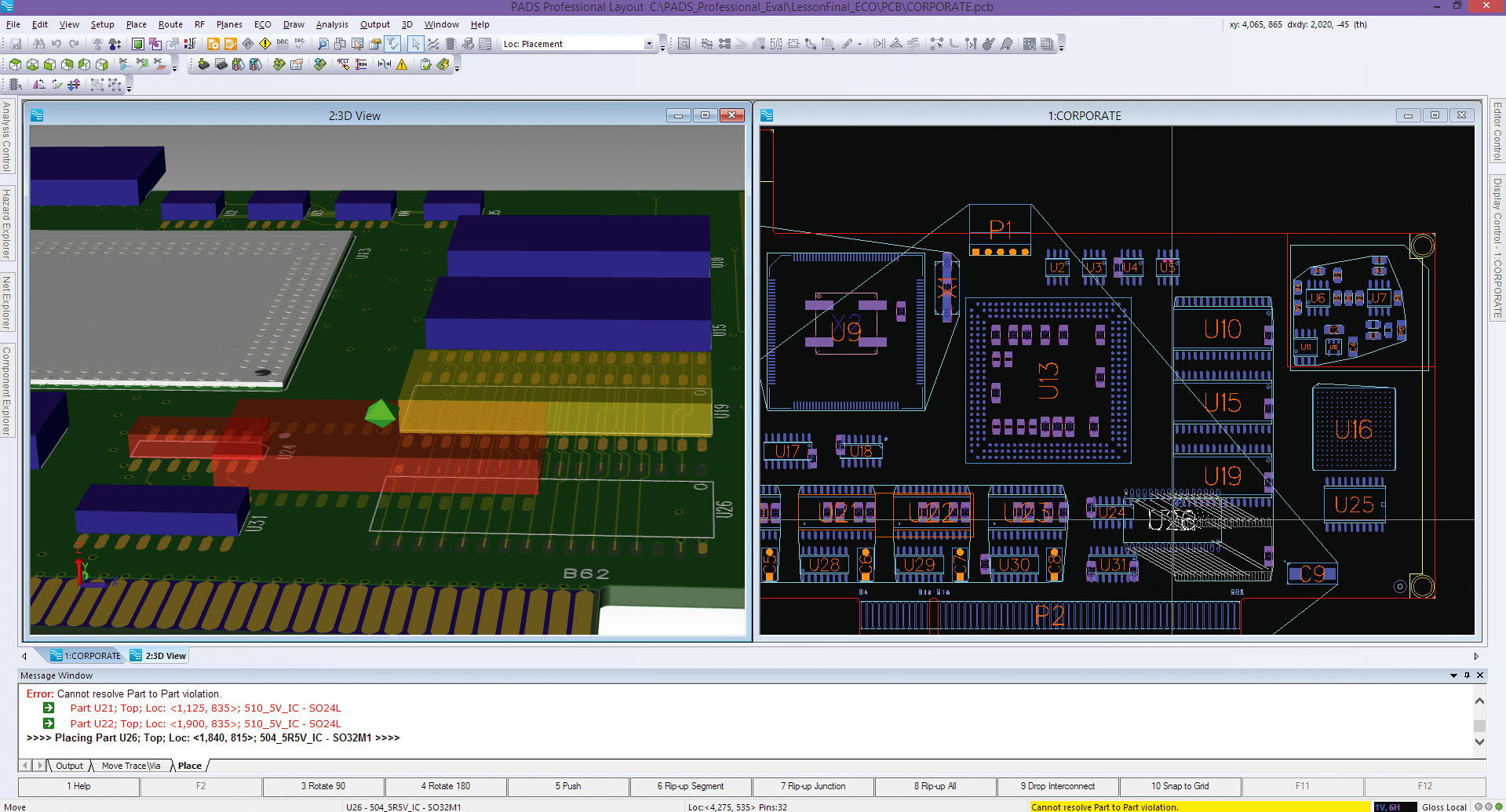

1 Установите общие зазоры для проекта, которые могут быть использованы в качестве шаблона для последующих дизайнов (рис. 3). Не забывайте задавать ограничения по всем координатным осям (X, Y, Z), чтобы система могла выявлять нарушения в размещении компонентов как в 2D, так и в 3Dрежимах (рис. 4).

Рис. 3. Ввод общих зазоров для проекта

Рис. 4. Проверка зазоров в 3D-режиме

2 Изучите документацию по наиболее значимым компонентам, используемым в проекте, и обратите особое внимание на шаг выводов контактных площадок и габаритные размеры. Это поможет определить минимальные значения для ширины проводников и зазоров между ними. Помните, что нужно учитывать технологические возможности производства и по возможности максимизировать ширину трасс и зазоров, чтобы избежать проблем на этапе изготовления.

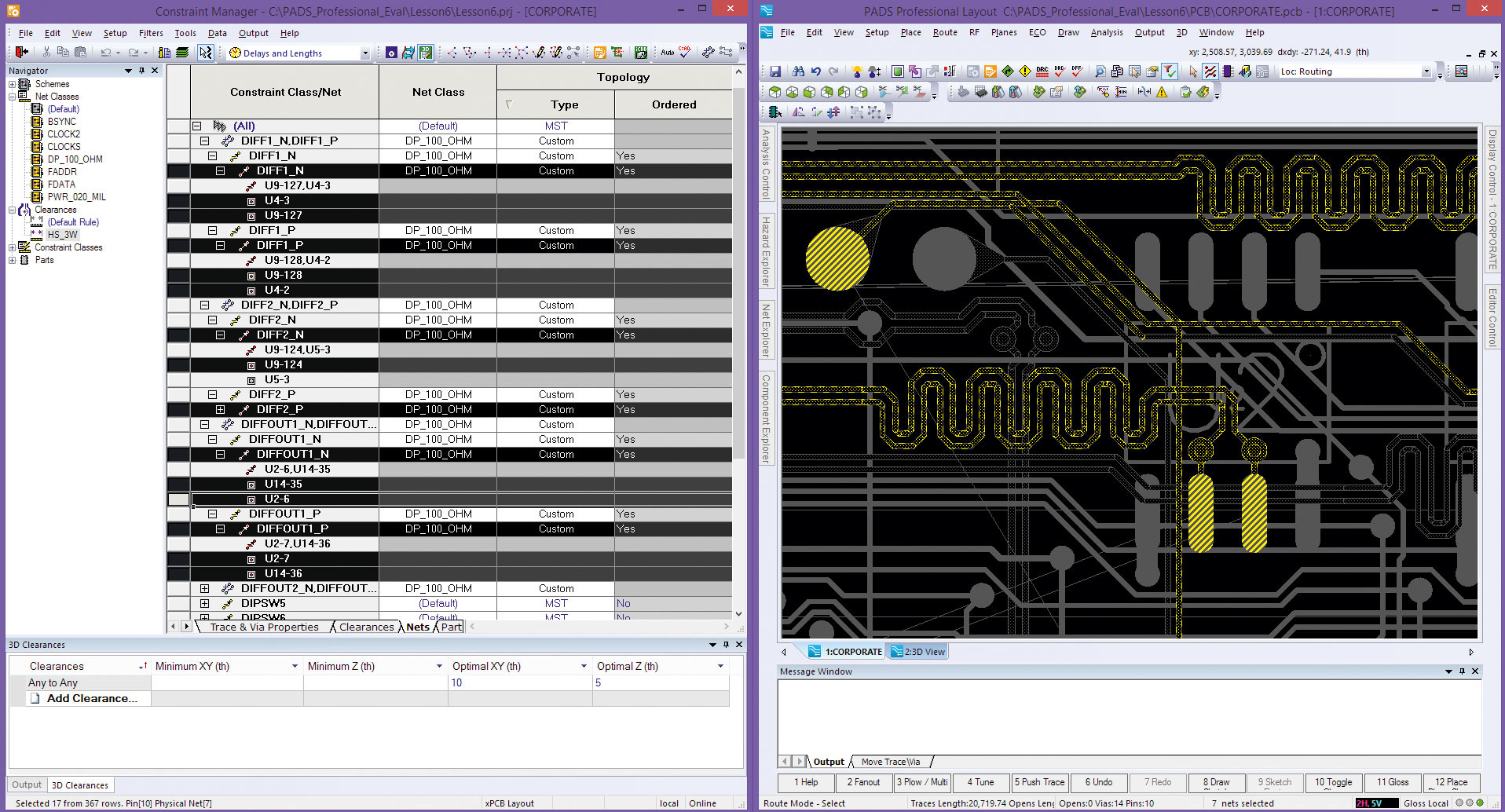

3 Определите, какие цепи являются критически важными в вашем проекте (DDR, PCIE, Ethernet, тактовые сигналы и др.) и установите для них правила, которые будут определять зазоры, задержки в линиях передачи и значения волнового сопротивления.

4 Установите максимальные и минимальные ограничения для каждого из этих требований. Они будут базовыми по умолчанию. Эти ограничения можно использовать для создания дополнительных классов.

5 Задайте дополнительные ограничения по зазорам для других известных условий, например правило 3W для высокоскоростных сигналов.

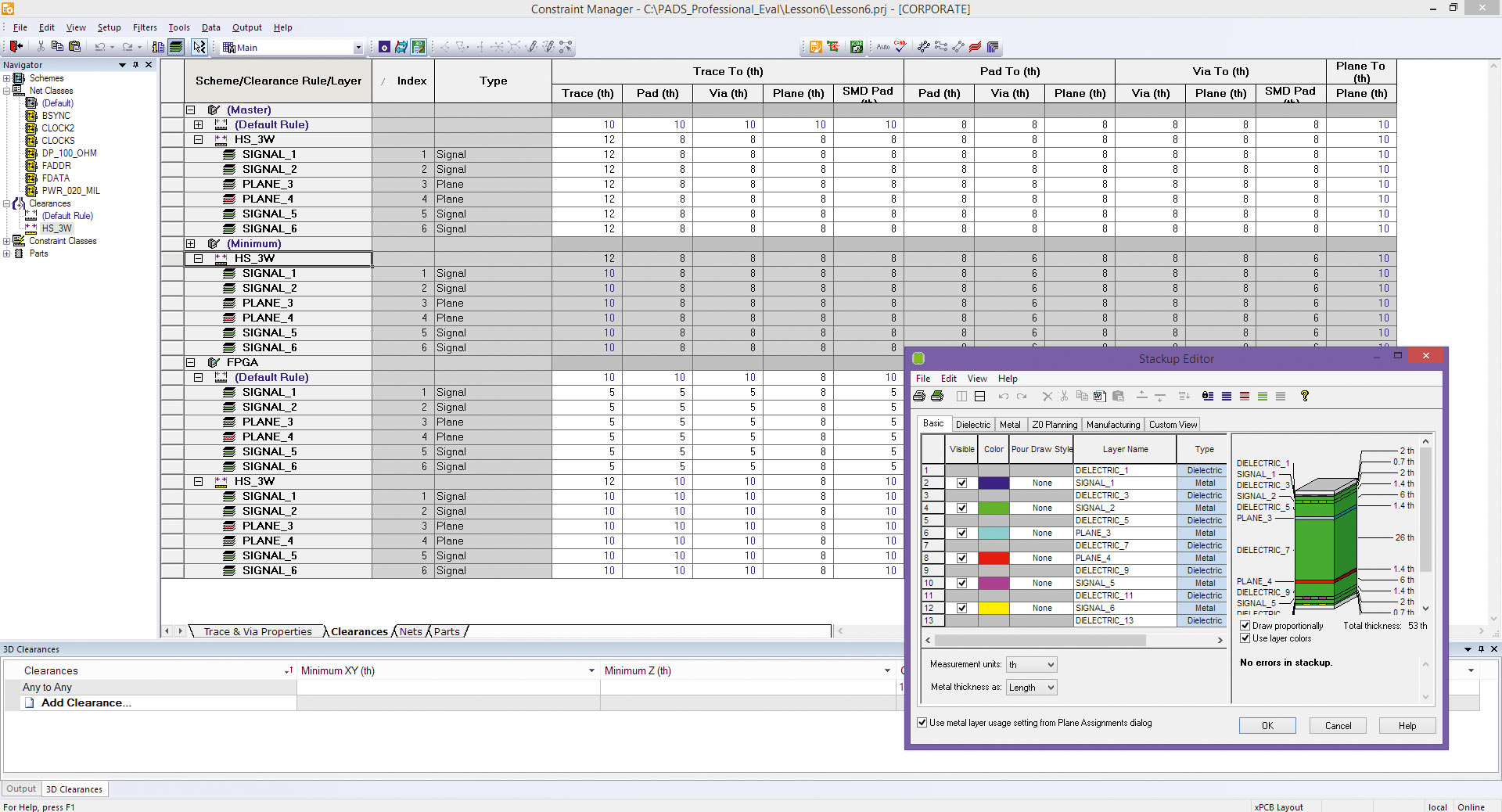

6 После того как все ограничения определены и заданы, создайте схемы или области для исключений (рис. 5). Каждая схема наследует ограничения из родительского класса, поэтому важно не создавать исключения до тех пор, пока ограничения не установлены.

Рис. 5. Создание областей для исключений после ввода ограничений

7 Создайте классы цепей для критических сигналов и установите зазоры между ними для обеспечения требований между каждым критическим классом (рис. 6).

Рис. 6. При заданных ограничениях критичных цепей их трассировка не вызывает проблем,

так как они мгновенно проверяются на соответствие правилам

8 Установите ограничения для остальных цепей, которые являются менее важными.

Используйте эти простые приемы в работе. Когда правильно настроена система ограничений, разработка плат — с момента создания схемы до финального этапа трассировки — происходит без сбоев. В результате повышается эффективность работы и сокращается время вывода готового продукта на рынок.

PADS — инструмент для достижения лучших результатов

Система управления ограничениями в PADS — интуитивно понятный, быстрый и надежный инструмент, разработанный специально для решения повседневных задач проектирования печатных плат. Унифицированный подход, используемый в PADS, обеспечивает эффективную методологию и позволяет избежать ошибок, возникающих при использовании сторонних средств управления ограничениями в схемотехническом и топологическом проектировании.

Ключевые преимущества PADS:

- расширенная система подсказок для облегчения использования программы;

- двунаправленное перекрестное выделение цепей и компонентов в системе управления ограничениями, а также схемном и топологическом редакторах;

- фильтры строк и столбцов, с помощью которых можно просматривать и быстро находить конкретные объекты и ограничения;

- интуитивная цветовая индикация нарушений обеспечивает визуальную обратную связь;

- иерархическая система наследования с автоматическим обновлением;

- встроенная синхронизация гарантирует, что все ограничения будут учтены.